基于天梯图分析的芯片性能发展轨迹及下一代技术面临的关键问题

- 问答

- 2025-09-30 18:17:19

- 1

爬梯子的焦虑与下一代技术的悬崖边

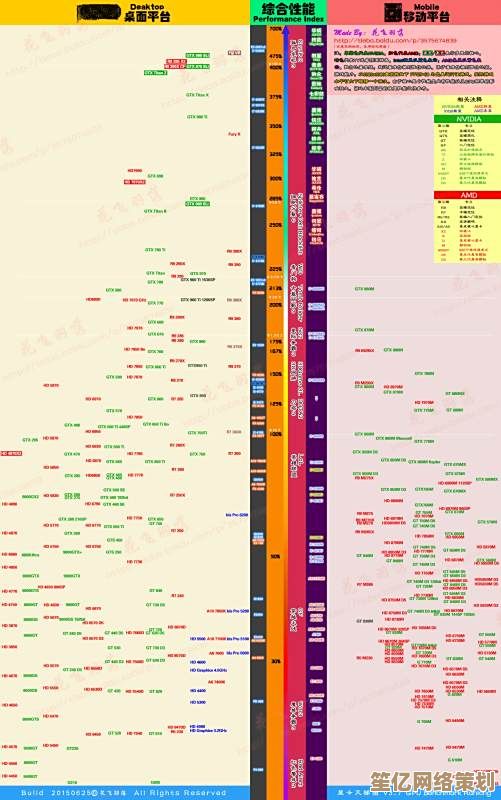

盯着屏幕上那条陡峭攀升的芯片天梯图曲线,我第N次陷入一种技术性眩晕🤯,这玩意儿像极了某种赛博朋克版本的“进度条”,从笨重的8086一路狂飙到如今指甲盖大小的怪兽,每一代都在叫嚣着“更快、更强”,可作为一个在实验室里被散热风扇噪音折磨了五年的硬件狗,我太清楚这华丽曲线背后,是工程师们用头发和咖啡因堆砌的叹息墙。

天梯图的“水分”与真实的“窒息感”

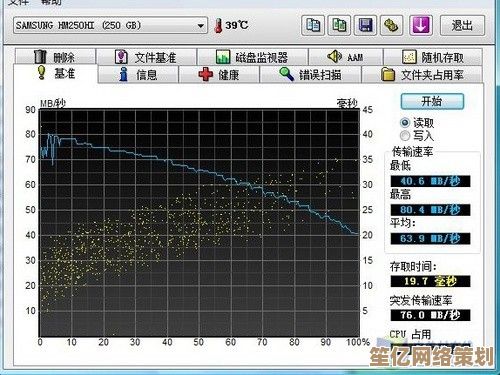

天梯图好看吗?好看,它把复杂的IPC、主频、功耗、跑分粗暴地压缩成一条简洁的“战力值”,让小白也能秒懂谁强谁弱,但它的“欺骗性”也在于此,去年我们实验室拿到某大厂旗舰移动芯片做测试,天梯图上它傲视群雄,跑分一骑绝尘,可当我们把它塞进一个接近真实使用场景(后台常驻微信、音乐、导航)的测试机里,连续跑半小时高负载游戏——那发热!那降频!🤬 性能曲线直接表演“高台跳水”,天梯图上那漂亮的峰值数字,瞬间成了橱窗里的模特——仅供瞻仰,日常穿出去完全不是一回事,这感觉,就像你看着米其林三星菜单流口水,结果端上来的菜量只够塞牙缝。

摩尔定律的“回光返照”与工程师的“土法炼钢”

“摩尔定律已死”的讣告写了快十年,可芯片巨头们硬是靠着各种“微创手术”在给它续命,台积电、三星在3nm、2nm节点上的缠斗,像极了两个武林高手在悬崖边比拼内力,每一丝精进都伴随着巨大的风险和成本飙升,EUV光刻机?那玩意儿贵得能买下我们整个研究所大楼🏢,而且娇气得像林黛玉,对环境要求苛刻到令人发指,记得有次行业会议,台积电一个工程师私下吐槽:“现在提升性能,60%的精力在跟物理定律搏斗,30%在跟成本算账,剩下10%才是‘创新’。” 这哪是造芯片,简直是精密到原子的“极限运动”。

更魔幻的是“土法炼钢”式的创新,当制程微缩的收益越来越薄,大家开始疯狂“堆料”和“叠罗汉”:

- 核战永不休: 手机SOC动辄“1+3+4”甚至更多核心集群,调度算法复杂得像解一道高等数学题,用户真的需要这么多核心吗?还是厂商在参数表上内卷的无奈?我手机里那个“小核”,感觉它一年到头都在摸鱼。

- Chiplet:硅片上的“乐高”🎮: 把大芯片拆成几个小芯片(Chiplet),用先进封装(比如Intel的EMIB、台积电的CoWoS)像拼乐高一样拼起来,AMD的Zen系列CPU靠这招翻身,性能功耗比确实惊艳,但这玩意儿对设计和封装的要求是地狱级的,良率?成本?想想就头大,上次听封装厂的朋友说,一个高端Chiplet封装良率波动能让他们老板一夜白头。

- AI加速器:专用“外挂”: CPU/GPU不够?那就加NPU、TPU!苹果的A/M系列、高通的Hexagon、谷歌的TPU,都是给AI计算开的“小灶”,效果拔群,但这也让芯片设计变成了一个更复杂的“联邦制”系统,软件生态的碎片化让人抓狂,调试一个涉及CPU+GPU+NPU协同工作的AI模型,那感觉就像在同时指挥交响乐团、摇滚乐队和广场舞大妈。

下一代:站在悬崖边,冷风嗖嗖

爬到现在这个高度,天梯图前方的路,雾气弥漫,冷风嗖嗖,关键问题像尖锐的岩石一样突出:

- “电老虎”与“火炉子”的终极对决: 性能提升的“油门”还在踩,但功耗和散热的“刹车”已经快踩断了!手机芯片峰值功耗冲上10W+,轻薄本芯片也能到百瓦级,再这么下去,手机真要变“暖手宝”,笔记本起飞变“直升机”了?🤯 新材料(GaN、SiC)、新架构(近存计算、存算一体)、甚至丧心病狂的“液冷手机”都在探索,但哪个能真正普及?我看实验室里那台咆哮的液氮超频装置,陷入了沉思——这玩意儿总不能塞进我裤兜吧?

- 先进制程:金钱与物理的双重绞索: 2nm及以下?量子隧穿效应带来的漏电问题,让工程师们夜不能寐,EUV光刻机只是门票,后续的工艺复杂度、良率控制、天文数字般的建厂成本(百亿美元起步!),让巨头们都肝颤,摩尔定律即使没“死透”,也绝对进入了“ICU”,靠砸钱和信仰续命,上周看到新闻说某厂2nm试产线光调试就花了半年,良率惨不忍睹,这成本最终还不是消费者买单?

- 设计复杂度的“诅咒”: Chiplet、异构集成、巨量IP核复用…设计一颗顶级芯片的复杂度和成本(人力、时间、EDA工具费用)呈指数级增长,芯片设计周期动辄2-3年起,流片失败一次足以让一个小公司破产,EDA巨头们(Cadence, Synopsys)的License费用贵得让我们所长每次签字手都抖,这高门槛,正在扼杀创新的多样性。

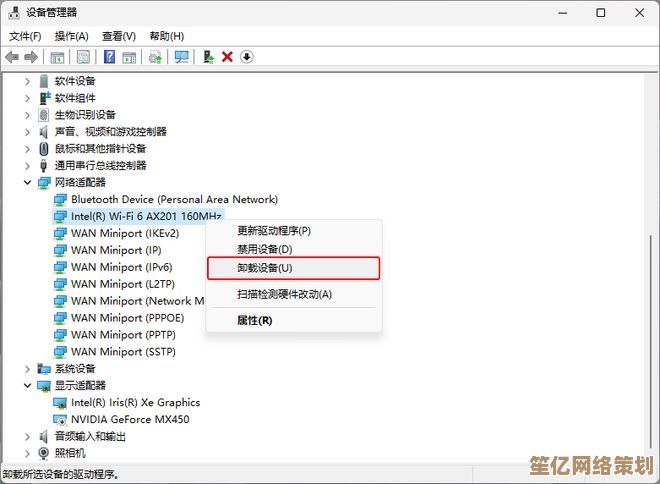

- 软件:被忽视的“短板”: 硬件再强,软件拉胯也是白搭,如何为异构计算(CPU+GPU+NPU+各种加速器)提供高效、统一、易用的编程模型和工具链?如何让开发者愿意投入?苹果的Metal和统一内存架构(UMA)是个好榜样,但生态壁垒太高,开源框架(如PyTorch, TensorFlow)在努力,但硬件差异带来的优化难题依然巨大,看着程序员同事为调优一个算子在不同硬件后端上的性能而秃头,深感软硬件协同的鸿沟有多深。

爬梯之后,路在何方?

芯片天梯图那根昂扬向上的线,还能画多久?它或许会逐渐放缓,变得崎岖,甚至在某一天彻底改变形态,下一代技术的突破,不再仅仅是晶体管数量的堆砌,而是一场涉及物理、材料、架构、封装、软件、乃至商业模式的“全面战争”,我们这些从业者,在仰望天梯图顶端的星辰时,脚下踩着的,是功耗的烈焰、制程的深渊、复杂度的荆棘和成本的寒冰,这攀登,注定伴随着焦虑、妥协与“土法炼钢”式的智慧。

也许,未来的芯片性能图谱,将不再是单一维度的陡峭天梯,而是一片需要多维能力(算力、能效、智能、成本)共同支撑的“高原”,爬不动“梯子”的时候,或许该想想怎么造“飞机”了?🚀 谁知道呢,反正我桌上的散热风扇,还在不知疲倦地嘶吼着,仿佛在说:“别想那么多,先搞定眼前这颗芯片的温控再说吧!” 这大概就是硬件工程师的日常浪漫(或者说,悲壮)?

本文由度秀梅于2025-09-30发表在笙亿网络策划,如有疑问,请联系我们。

本文链接:http://waw.haoid.cn/wenda/15042.html